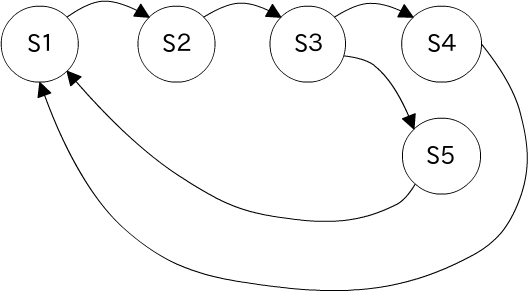

状態遷移図

今回は前回作成したスタックマシン型のCPUをVerilogで実装する。そのためにCPUの動作を表した状態遷移図の作成を行った。

状態遷移図の各状態での動作は以下に示す通りである。

- 命令フェッチ

- 命令デコード

- データフェッチ

- データ操作命令実行

- 演算命令実行

である。S1ではプログラム・カウンタの値から命令の読み出しを行う、S2では命令の解釈を行う、S3では必要であればデータのフェッチを行う、S4とS5は命令の実行であり、S4ではデータ操作命令の実行、S5では演算命令の実行を行う。

メインメモリに二度アクセスするPush命令とPop命令を除き、命令の行う処理は1サイクルで実行できる内容であるが、デバッグのしやすさと、動作の理解のしやすさを考え、マルチサイクルで命令の実行を行う。

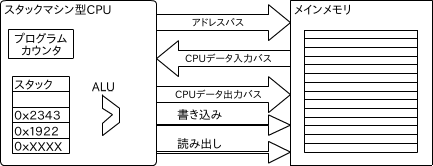

コンピュータシステムの構成

CPUだけではコンピュータとして成立せず、プログラムを実行できないので、CPUにメインメモリを接続する。このメインメモリには初期状態では実行するプログラムや、プログラム上で扱う定数などが格納されている。またプログラム実行時の変数等もメインメモリ上で扱われることになる。

メインメモリとCPUは10bitのアドレスバス、16bitのCPUデータ入力バス、16bitのCPUデータ出力バス、1bitのメモリ制御信号により接続される、

アドレスバスはメモリ上のデータを参照したり、メモリ上でデータを格納したり、する時にメインメモリ上のアドレスを指定するために使用される。CPUデータ入力バスはメインメモリからデータを読み出すのためのデータバスである。CPUデータ出力バスはCPUからメインメモリへデータを書き出すためのデータバスである。メモリ制御信号はメインメモリに対して行う操作を書き込みか、読み込みか指定するために使用される。今回の場合は読み込み/書き込みどちらの線を1にしたかで動作をしてできるようにする。

バスの動作は例えば0x0ff番地にデータ0x0064を書き込みたい場合は、アドレスバスを0xffに,CPUデータバスに0x64を指定し、書き込み信号を1にすれば良い。この状態でシステムクロックの立ち上がりが発生すると指定したアドレスにデータの書き込みが行われる。