本稿はSRAMに関するお話です。はっきり言ってしまえばSRAMはHDLには関係ありませんね、ですが皆さんSRAMはよく使うと思うので理解していて損はないと思います。LSI焼くときに役に立つと思いますので。 とりあえずここでは一週間遅れてしまったことをお詫びします。

SRAMについての基礎知識

SRAMはStatic Random Access Memory略してSRAMです。基本的にプロセッサ内のキャッシュや、スクラッチパッドメモリ、マイクロコントローラのメモリなどはSRAMで構成されています。SRAMの基本的な特性としては以下のようなものです。

- 😄回路が単純であるためDRAMと比較して読み書きが高速である。

- 😄リフレッシュが不要であり、読み書きを行わない場合、基本的にリーク電流以外が流れないためDRAMより少電力である。

- 😞4つか6つ以上のトランジスタにより構成されるため、DRAMやMRAMより回路面積が大きい

- 😄トランジスタで構成されているためフラッシュメモリやDRAMと異なり、プロセッサと同じプロセスで製造することが出来る(ココ重要)

- 😞DFFなどで構成されるレジスタと異なり、アナログ回路とデジタル回路の中間的存在であり読み出しに周辺回路が必要。(ココ重要)

特に重要な点はCPUと同じプロセスで製造することが出来る点です。このおかげで、LSIを構成する一つのシリコン上にSRAMとCPUやその他デジタル回路を同居されることが可能であり、デジタル回路からの高速で広いビット幅でのアクセスが可能です。FPGAにおけるBRAMみたいなものだと思っておけばよいでしょう。

メモリ全体におけるSRAMの立ち位置を明らかにするために、高密度でおそらく最もよく使われるRAMの一種であるDRAMと、最近注目が集まっているMRAMとも比較を行いました。 表にまとめると次のような感じになります。 最近はMRAMも性能を上げてきていて、枯れたプロセスであればSRAMよりMRAMの面積が小さいため、「プロセッサの内部キャッシュをMRAMで製造しよう」みたいな話も出てきていますが、基本的にシンプルなSRAMがデファクトとなっています。 今後も手軽に製造可能なSRAMが他のメモリに取って代わられることは当分無いでしょう。

| メモリの種類 | SRAM | DRAM | MRAM |

|---|---|---|---|

| リフレッシュ | 不要 | 必要 | 不要 |

| 速度 | ◎ | △ | ○ |

| 面積 | 6T | 1T | 1T |

| 不揮発性 | ☓ | ☓ | ◎ |

| ロジックとの同居 | ◎ | ☓ | 特殊 |

SRAMのメモリセル

SRAMはデコーダ、プレチャージ回路など様々な回路で構成されていますが、その中で中核を成す最も重要な要素はメモリセルです。

メモリセルはデータを記録する回路であり、ふたつのインバータから構成されるクロスカップルドラッチとアクセス用のトランジスタから構成されます。クロスカップルドラッチは、2つのインバーターがリング状に接続された構造になっています。この場合偶数段のインバーターチェーンであるので安定した状態を保持します。

昔の半導体設計ではPMOSの性能が出なかったためインバータの上段を抵抗で構成することも多かったようですが、現在のプロセスではPMOSもかなり良い性能を達成可能であるのと、先端プロセスにおいては抵抗値を稼ぐことが難しくなっていることや、上段抵抗であると電源電圧を下げにくいなどの難点もあります。よって、現在は基本的にプッシュプルインバーターが使われています。

余談ですが、面積を向上させるための二階建てSRAMとか、アクセストランジスタが複数あるマルチポートSRAMとか奇抜な構造のものもいろいろありますが、ここでは語りきれないので気になったらぜひ論文を漁ってください。

SRAMのメモリセルの読み書き操作

SRAMのメモリセルの構造を見ると、基本的な電子回路の知識がある人は「情報が記録できる原理は理解できるけど、こんなものからどうやってデータを書き込んだり、読み出したりするんだ?」と疑問に思うに違いません。このセクションではまず、メモリセルの簡単な全体像について述べて、その後、SRAMの読み書き操作について述べます。

図2に示すようにクロスカップルドラッチに対して読み出し用のポートを付けたものがメモリセルです。クロスカップルドラッチを構成するインバータの出力と入力の間に、アクセストランジスタが接続されており、メモリセル一つあたり6個のトランジスタで構成されることになります。これが6TSRAMと呼ばれる理由です。

メモリセルにはワード線(WL)とビット線(BL)という2種類のポートがあります。

WLはメモリセル自体を選択するためのものです。メモリセルに書き込んだり、メモリセルからデータを読み出すタイミングでこのWLがHighになります。メモリとして動作する場合、基本的にアドレスのデコーダに接続されています。BLはデータそのものが流れる回路です。メモリセルはインバータなのでBLと反転した〜BLの二本が存在し、差動で動作します。単純な構造のSRAMではSRAMではビットラインを介してデータの読み込みと書き込みの両方が行われますが、デュアルポートSRAMなどでは、別に読み出し用のトランジスタが設置される場合もあります。

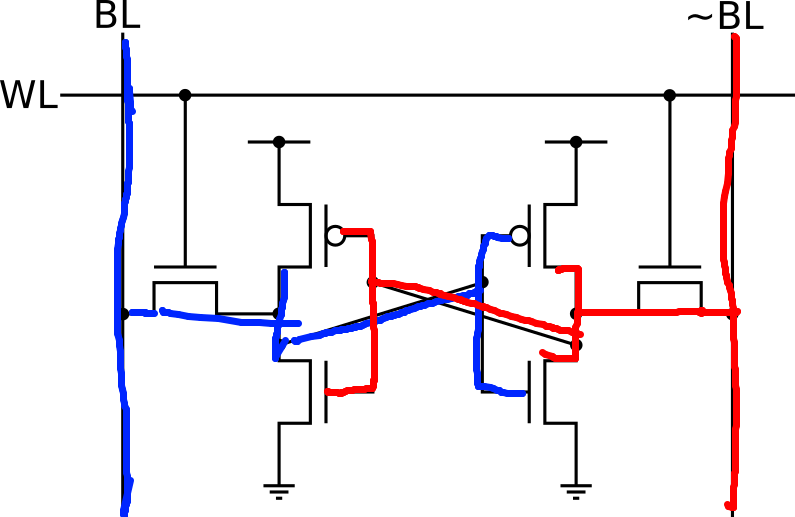

SRAMのメモリセルの書き込み

SRAMの書き込みは読み出しに比べると非常に簡単な操作です。読み書きを行いたいメモリセルのワード線に電圧を印加した上で、BLに書き込みたいデータの電圧を印加して、クロスカップルドラッチの状態を無理やり書き換えるだけです。図3にデータ書き込み時の電圧の印加の様子を示します。赤く塗られている線は電圧がHigh、青く塗られている線は電圧がLow電圧が印加されています。 この図の場合ですとBLがLow、~BLがHighが印加されていますので、書き込まれているデータは0になりますね。 このような電圧が印加されると、安定しているクロスカップルドラッチの状態が無理やり書き換えられることになります。最初に見たときはなかなかびっくりしましたが、非常に少ないトランジスタで必要な機能を実現できている面白い方法だと思います。

SRAMのメモリセルの読み出し

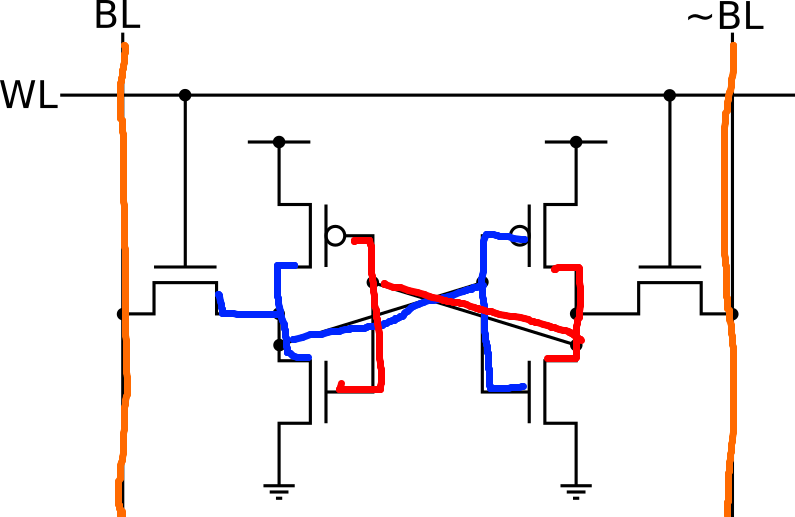

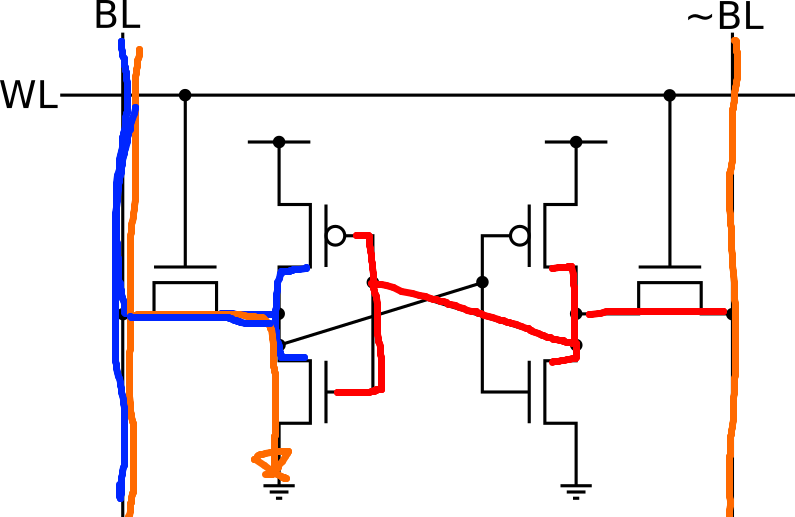

SRAMの読み出しは書き込み操作と比較すると幾分複座雑です。というのも、SRAMはデジタル回路とアナログ回路の性質を併せ持つ回路であり、特に読み出し操作に関してはアナログ的な性質が大きく現れるからです。SRAMの読み出し操作は以下のプレチャージ、データ読み出し、ラッチの3ステップで説明します。

1. プレチャージ

SRAMの読み出しはクロスカップルドラッチからのデータの読み出しは、書き込みでも利用されたビットラインから行われます。すべてのワードラインをLowにした状態で、プレチャージ回路からビットラインビットラインをに電圧を印加します。この状態で、プレチャージ回路をHiZ状態、つまり、高抵抗状態に切り替えると、ビットラインをコンデンサとみなしたときに、配線に電荷がチャージされた状態になります。この操作をプレチャージと呼びます。

2. データの読み出し

データ読み出しではメモリセル、つまりクロスカップルドラッチを使って、プレチャージされた放電することで実現されます。読み出し対象のメモリセルのワードラインをHighすると、クロスカップルドラッチとプレチャージされたBLおよび〜BLが接続されます。するとクロスカップルドラッチのうち、Lowが設定されている方にプレチャージされた電荷が吸い込まれることになります。これにより、BLおよび〜BLは反転した状態になります。このビットラインをオペアンプやコンパレータなどの差動読み出し回路に入力すればデータの読み出しが実現できます。

3. データの読み出し

最後に差動読み出し回路の出力をラッチします。これにより読み出したデータを、アナログ世界からデジタル世界に確定することなります。

以上がメモリの読み書きの操作になります。

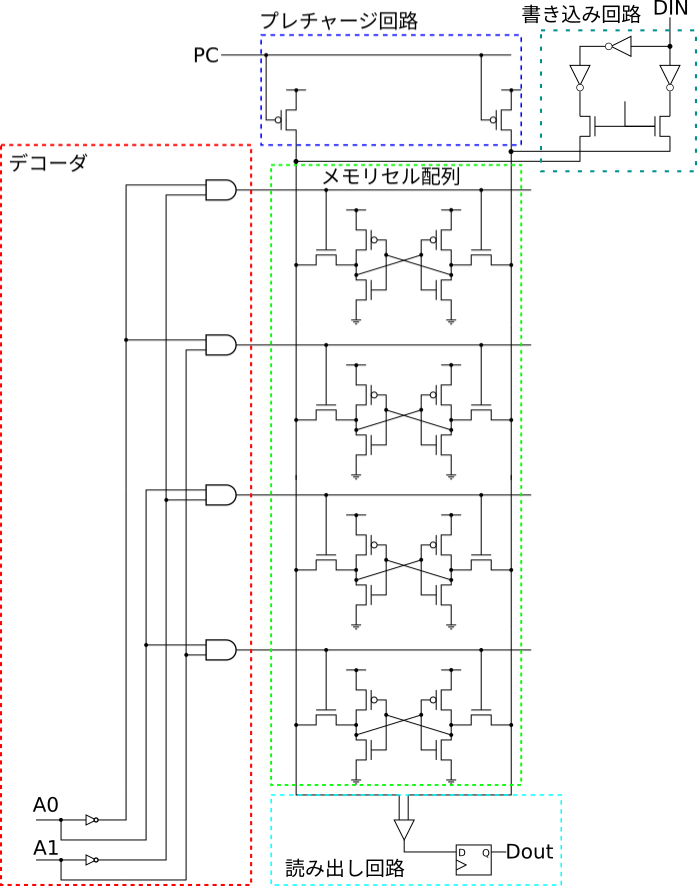

SRAMのメモリマクロ

SRAMここまでメモリセルに対する読み書き操作に関する話をしてきました。メモリセルはデータを記録することができる回路ですが、読み出しや書き込みには別の回路が必要となります。また、メモリセルだけではアドレッシングができないためアドレスのデコーダ回路なども必要となります。このような、みなさんが普段使うSRAMとして動作するのに必要な回路をひとまとめにしたものをメモリマクロと呼びます。

次の図にメモリセルのアレイと、周辺回路を含めたメモリマクロの図を示します。メモリマクロというのは半導体設計をしたことがある人は知っていると思いますが、いわゆるマクロであり、特定の機能をまとめた回路のブロックです。SRAMは純粋なデジタル回路と異なりアナログ回路であるため配線長やノイズの影響を受けやすくP&Rで配置配線出るわけではないので、アナログ回路としてメモリコンパイラや手配線で設計してあげる必要があります。

メモリマクロの構成要素について説明します。今回の説明では話をわかりやすくするために簡略化していますが、図に示すメモリマクロの構成要素はメモリセル配列、アドレスデコーダ,プレチャージ回路,書き込み回路,読み出し回路です。ここにカラムセレクタが追加されることもありますが、私はカラムセレクタが載ったメモリセルを設計したことがないため説明を省略します。

次にそれぞれの要素について説明してゆきます。

メモリセル配列

メモリセル配列はメモリセル複数並べたものになります。メモリセル配列内では縦方向にビットラインを、横方向にワードラインを共有した構造となっています。ビットラインを共有するということは、一つのデータのうちMSBからLSBからのどのビットに相当するかという信号を共有していますので同じビットラインに接続されたメモリセルはワード内の同じビットということになります。また、横方向のメモリセル同士はWLを共有しています。つまり同じ行に属するメモリせるは同じワードを構成するビットであるということになります。今回、図として示している画像はアドレスが2bit、ワードも2bitですが、例えば16bitアドレスの8bitワードのメモリマクロであれば、メモリセル配列は65536の行を持ち、横方向には8個のメモリセルが並び、8本のBLおよび~BLを持つ事になります。ただし、このような配線を愚直に行うと配線長が長すぎて抵抗値が増大して読み出しが遅くなので列を分割してカラムセレクタでセレクトするなど工夫が必要です。

アドレスデコーダ

アドレスデコーダは名前の通り、データのアドレスをWLに変換するための回路です。基本的にはNOT回路とAND回路で構成され、行に対応するアドレスが入力された場合に、そのアドレスに相当するWLが1になる回路が、それぞれの行ごとに構成されています。ただ、この構成ですと、回路が大規模化したときに、配線長が長くなりすぎたり、回路に接続されたAND回路の数が増えすぎて、ファンアウトが肥大化ししてしまいます。これを避けるために、実際のメモリマクロではデコーダを、WLに直結されたAND回路であるデコーダと、その前段としてよりアドレス入力に近い位置に設置されたプリデコーダに分けて実装します。これにより最集段のファンイン(配線にぶる下がるロジック入力の数)を制限したり、デコーダの回路規模を抑制してデコード速度の低下を抑えることに繋がります。

プリチャージ回路

BLおよび〜BLをプリチャージするための回路となります。大量のWLのアクセストランジスタがぶら下がっているBLおよび〜BLを駆動するための回路であるので、それなりのパワーが必要となります。この回路の出力はBLと〜BLを電源電圧に釣り上げるためのオン状態と、チャージ状態を維持すためのHiZ状態の二種類となります。

読み出し回路

センスアンプはBLの状態から、データを読み出すための回路です。メモリセルの説明で述べましたが、BLおよび〜BLは反転した電圧となるため、差動で読み出すことになります。この読み出した信号をラッチで確定することにより読み出しデータが確定します。 余談ですが、このセンスアンプ部分は差動ではコストが高いので、マルチポートSRAMなどでは基準電圧を使ったシングルエンド読み出し回路が実装されることもあります。このような場合読み出し速度は当然差動式に劣ることになります。

書き込み回路

メモリセルに対してデータを書き込むための回路です。メモリセルのBLは長くなりがちなので、BLを上げ下げするのに十分なパワーを得られるようにファンアウトしてあげる必要があります。

まとめ

メモリセルの簡単な説明を行いました。本当はOpenMPWのPDKで設計からシミュレーションまで行って記事にまとめたかったのですが、間に合いませんでした。 アドベントカレンダーの運営者様、および他の参加者様にはここで重ねて遅れたことをお詫びします。